无论是 SmartNIC、还是密集的服务器互联拓补,都依赖于 FPGA 开展初始部署和调整,然后才会转向 ASIC 。

长期以来,Xilinx 和 Altera(已被英特尔收购)一直在努力压过对手一头,将收发器速率从 26G / 28G,一路推升到了 56G / 58G 。

2018 年的 Arch Day 大会上,英特尔更是介绍了选用 116G 收发器的 M-系列 10nm Agilex FPGA 方案。

据悉,基于以太网的 116G“F-Tile”是一个独立的小芯片模块,通过嵌入式多芯片互连桥接(EMIB)技术与中央 Agilex FPGA 相连,并且采用了与主 FPGA 芯片不同的制程工艺。

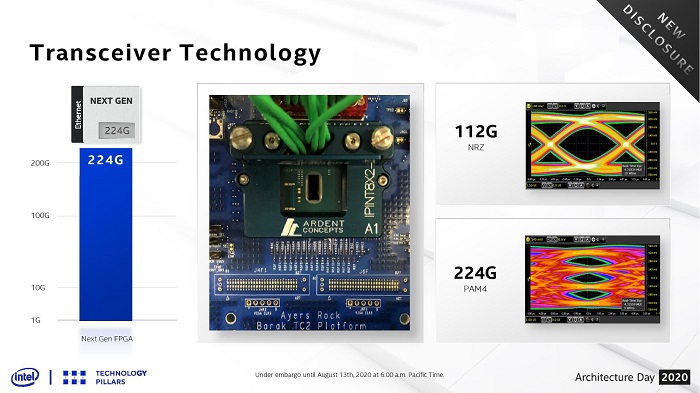

而作为 2020 英特尔架构日活动的一部分,该公司宣布其正在开发一款标称速率达 224G 的新型收发器模块。其不仅支持 PAM4 模式下的 224G 收发(4-bit),还支持 NRZ 模式下的 112G 收发(2-bit)。

英特尔表示,新模块使得下一代以太网协议栈成为可能,该公司计划在 2021 / 2022 后期准备就绪,并且向后兼容 Agilex 的 100 / 200 /400 GbE 栈。至于误码率或功耗等更多细节,目前暂不得而知。